เมื่อวันที่ 4 พฤษภาคมที่ผ่านมา อินเทลได้ทำการเปิดตัวเทคโนโลยีในการผลิตชิปหน่วยประมวลผลแบบ 22 นาโนเมตร ซึ่งเทคโนโลยีในการผลิตแบบ 22 นาโนเมตรนี้ก็จะเข้ามาแทนที่การผลิตแบบ 32 นาโนเมตร ในช่วงปลายปี 2011 นี้ และตาม Roadmap ที่เราทราบก็คือ Ivy Bridge จะเป็นซีพียูตัวแรกที่ผลิตด้วยกระบวนการ 22 นาโนเมตรนี้ แต่ว่าสถาปัตยกรรมหลักๆ ภายในของซีพียูนั้น ยังคงเป็นแบบเดียวกับ Sandy Bridge

Tick-Tock Model ของอินเทล ในรูปนี้แสดงให้เราเห็นว่าถึงช่วงเวลา Tick แล้ว ซึ่งตามปกติแล้วในช่วง Tick ก็จะหมายถึงช่วงเวลาในการเปลี่ยนแปลงกระบวนการผลิตซีพียูโดยที่ยังคงใช้สถาปัตยกรรมแบบเดิม ส่วนช่วง Tock จะเป็นช่วงการเปลี่ยนแปลงสถาปัตยกรรม

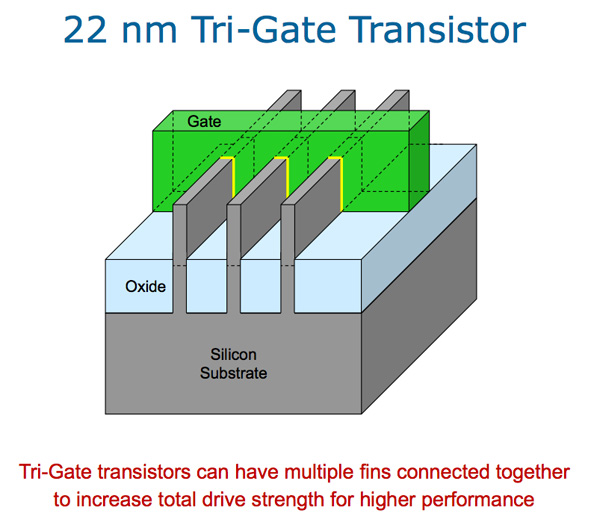

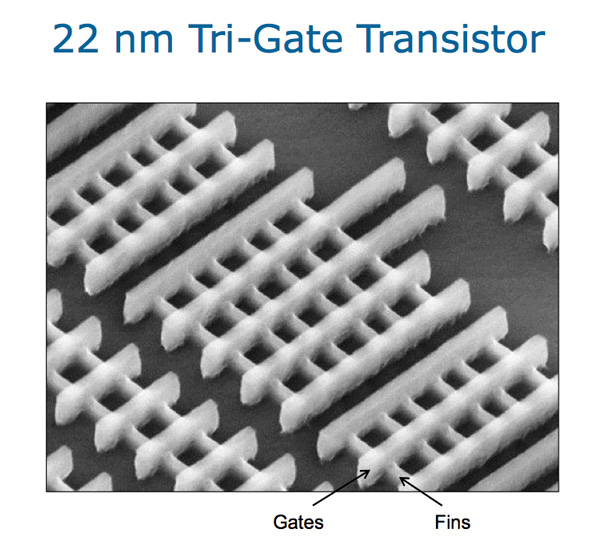

ความพิเศษในการเปิดตัวการผลิตชิปด้วยกระบวนการ 22 นาโนเมตรนี้อยู่ที่กระบวนการผลิตทรานซิสเตอร์ที่อยู่ภายในซิลิกอน โดยอินเทลเรียกทรานซิสเตอร์แบบใหม่นี้ว่าเป็น 3D Transistor และถ้าเป็นการผลิตซีพียูรุ่นใหม่ก็จะใช้ 3D แบบ Tri-gate อีกด้วย

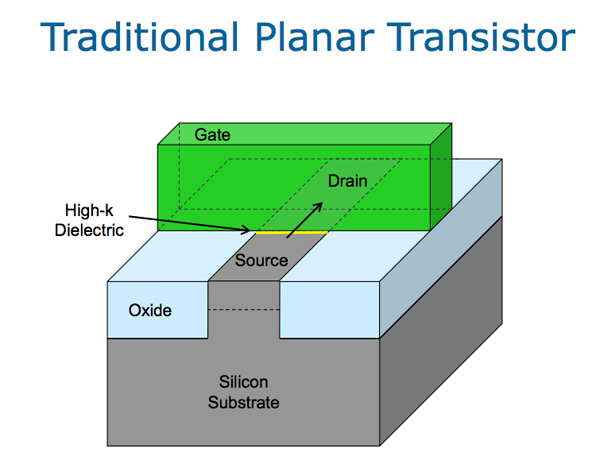

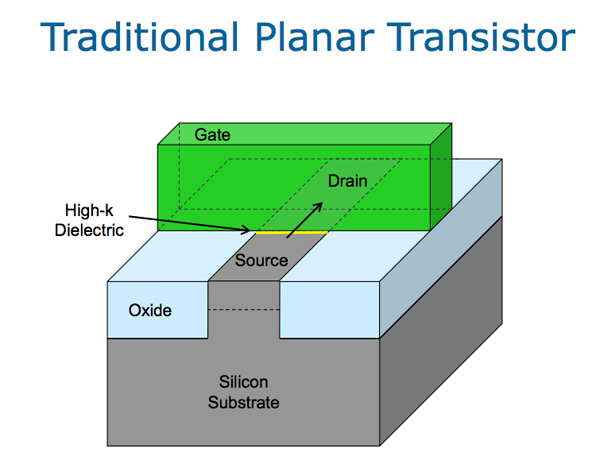

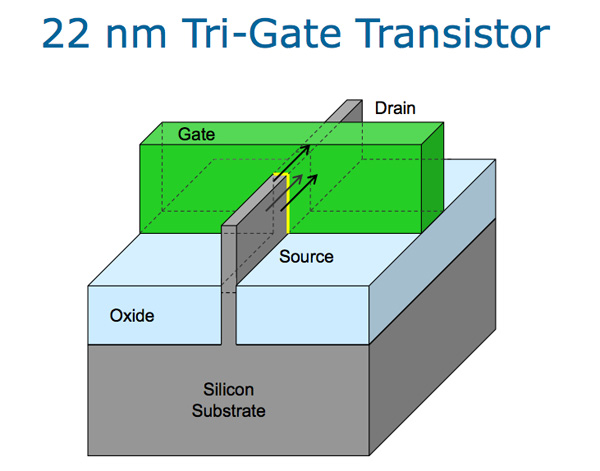

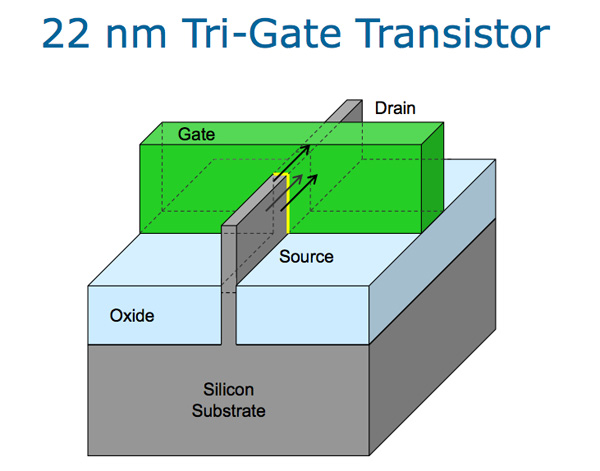

รูปด้านบนนี้คือลักษณะจำลองของทรานซิสเตอร์แบบเดิม ซึ่งเราจะเห็นได้ว่าพื้นที่ที่ให้กระแสไฟฟ้าไหลผ่านทรานซิสเตอร์นั้นมีลักษณะเป็นพื้นที่แบบกว้าง x ยาว หรือเป็นแบบ 2D ส่วนรูปถัดไปคือลักษณะของทรานซิสเตอร์แบบ 3D ที่มีการเพิ่มพื้นที่ช่องทางการไหลของกระแสไฟฟ้าในแบบ กว้าง x ยาว x สูง

จากในรูปเราจะเห็นได้ชัดเจนกว่าทรานซิสเตอร์แบบ 3D นั้นจะมีพื้นที่ให้กระแสไฟฟ้าเดินทางผ่านได้มากกว่าทรานซิสเตอร์แบบ 2D และการที่มีพื้นที่ให้กระแสไฟฟ้าไหลผ่านมากขึ้นนั้นจะช่วยให้เกิดประโยชน์คือลดแรงเสียดทานในระหว่างการไหลของกระแสไฟฟ้า เมื่อลดแรงเสียดทานได้แล้วผลที่ตามมาก็คือการใช้พลังงานที่ลดลง รวมไปถึงการเกิดความร้อนในการทำงานที่น้อยลงด้วย

และเมื่อเกิดความร้อนน้อยลงสิ่งสำคัญที่ตามมาก็คือ เราสามารถเร่งความเร็วในการสวิตช์ (On/Off – 1/0) ของตัวทรานซิสเตอร์ได้มากขึ้น หรือเพิ่มความถี่ในการทำงานให้กับตัวชิปได้มากขึ้นนั่นเอง

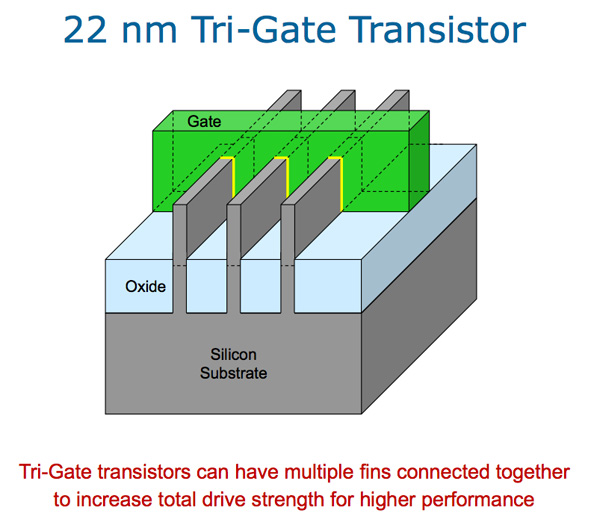

แต่สิ่งที่น่าสนใจไม่ได้อยู่ตรงที่เป็น 3D ทรานซิสเตอร์เท่านั้น แต่อินเทลยังได้ทำการเพิ่มจำนวน Gate ในทรานซิสเตอร์แต่ละตัวให้มีถึง 3 Gate นั่นก็ทำให้ลดความร้อนและลดการใช้พลังงานได้เพิ่มขึ้นไปอีก ซึ่งการเพิ่มจำนวนเกตเข้าไปนี้ก็เป็นผลมาจากความสามารถของกระบวนการผลิตที่เล็กลงในระดับ 22 นาโนเมตรนั่นเอง (จึงเป็นที่มาของคำว่า Tri-gate Transistor)

รูปด้านบนนี้แสดงถึง ความก้าวหน้าของเทคโนโลยีในการผลิตซีพียูจากเทคโนโลยี 90 นาโนเมตร ในปี 2003 มาถึงเทคโลยีแบบ 22 นาโนเมตร ในปี 2011 ซึ่งการพัฒนาในแต่ละช่วงจะใช้เวลาประมาณ 2 ปี ในปี 2007 อินเทลได้เพิ่มวัสดุการผลิตแบบใหม่เข้าไปเรียกว่า High-k Metal gate ให้กับทรานซิสเตอร์ และในปี 2011 นี้ ได้เพิ่ม 3D Tri-Gate เข้าไป

ภาพการทำงานจริงของทรานซิสเตอร์ 2D แบบเก่า จะเห็นเส้นเล็กๆ บางๆ แนวระนาบ แทนการวิ่งของอิเล็กตรอน

ส่วนทรานซิสเตอร์ 3D Tri-Gate แบบใหม่ เส้นจะนูนขึ้นมา

สำหรับเทคโนโลยี Tri-Gate นั้นอินเทลได้เริ่มทำการวิจัยและพัฒนามาตั้งแต่ปี 2002 และทดลองนำมาผลิตกับชิปหน่วยความจำเป็นครั้งแรกในปี 2006 จากรูปนี้จะเห็นได้ว่าอินเทลมีวิสัยทัศน์ในการพัฒนากระบวนการในการผลิตชิปเป็นอย่างมาก และทำให้เราแปลกใจได้เมื่อคิดว่าการพัฒนากระบวนการผลิตชิปในแบบซิลิกอนกำลังถึงทางตัน แต่อินเทลก็ได้พิสูจน์ให้เห็นว่าการผลิตชิปด้วยซิลิกอนนั้นยังมีอนาคตและยังสามารถพึ่งพาได้ จนกว่าเทคโนโลยีการผลิตชิปแบบ Bio หรือเทคโลยีแสงจะเป็นจริงและมีราคาถูกลง

โรงงานที่อินเทลจะใช้ในการผลิตซีพียูแบบ 22 นาโนเมตร

อินเทลจะนำเทคนิคการผลิตแบบนี้ไปใช้กับซีพียูรุ่นถัดไปรหัส Ivy Bridge ซึ่งผลิตที่ 22 นาโนเมตร ซึ่งเมื่อเทียบกับทรานซิสเตอร์แบบเดิม ผลิตที่ 32 นาโนเมตรแล้ว ประสิทธิภาพจะดีขึ้น 37% หรือในทางกลับกันคือกินไฟน้อยลงครึ่งหนึ่ง หรือ 50 %

เทคนิคการผลิตแบบนี้จะช่วยให้อินเทลยังรักษา "กฎของมัวร์" ต่อไปได้อีกระยะหนึ่ง

ที่มา

http://www.quickpcextreme.com

http://www.blognone.com

http://www.anandtech.com